Das Programm beschraenkt sich auf die relevanten Taetigkeiten zur verlustbehafteten bauteilnahen Auslegung von Power Topologien und zugehoerige Regler.

Die erfolgreiche Bedienung des Programmes erfordert das entsprechende regelungstechnische und mathematische Grundwissen:

1. Regelstrecken, Regler

2. Uebertragungsfunktion

3. Pol/Nullstellenberechnung und deren Bedeutung in der Regelungstechnik

4. Frequenzgang

Das Programm liefert:

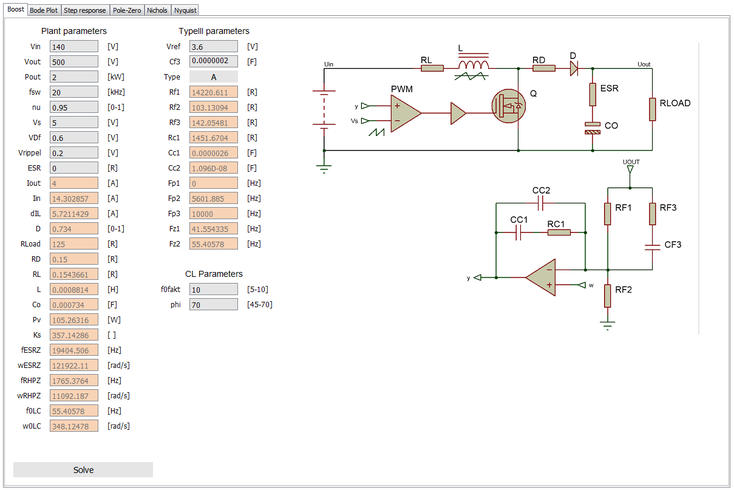

1. Berechnung aller Relevanten Topologiebauteile.

2. Berechnung der Verlustwiderstaende sowie Schalt- und Leitverluste.

3. Auswahl der geeigneten Regler und Reglerstruktur.

4. Parametrierung der Regler.

5. Parameter fuer digitale Reglerimplementierung.

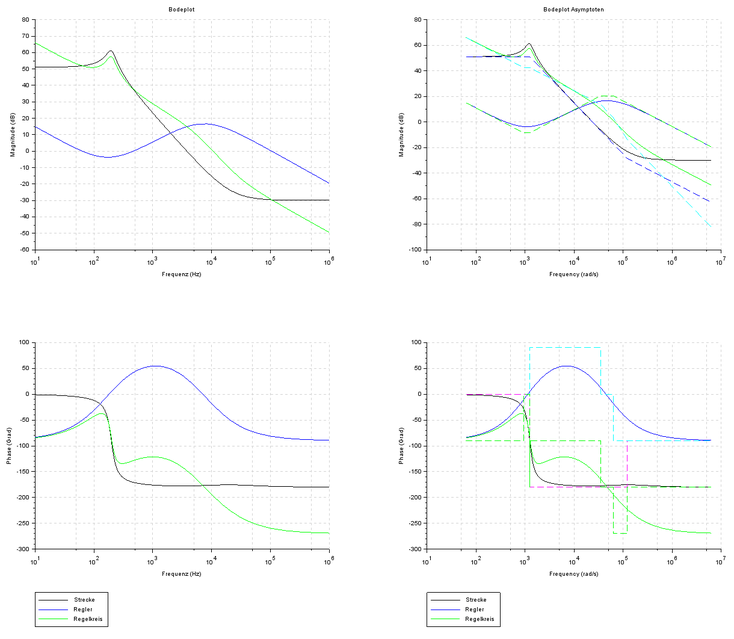

6. Vergleich der Topologie mit verschiedenen Regler- und Streckenparameter.

7. Vergleich analoger - digitaler Regler bei gegebener Strecke/Topologie.

8. Sprungantowrt der Strecke.

9. Sprungantwort des open loop Kreises (Gs(s)*Gr(s))

10.Sprungantwort des Regelkreises (Gs(s)*Gr(s) / (1+(Gs(s)*Gr(s)*Gfb(s)))

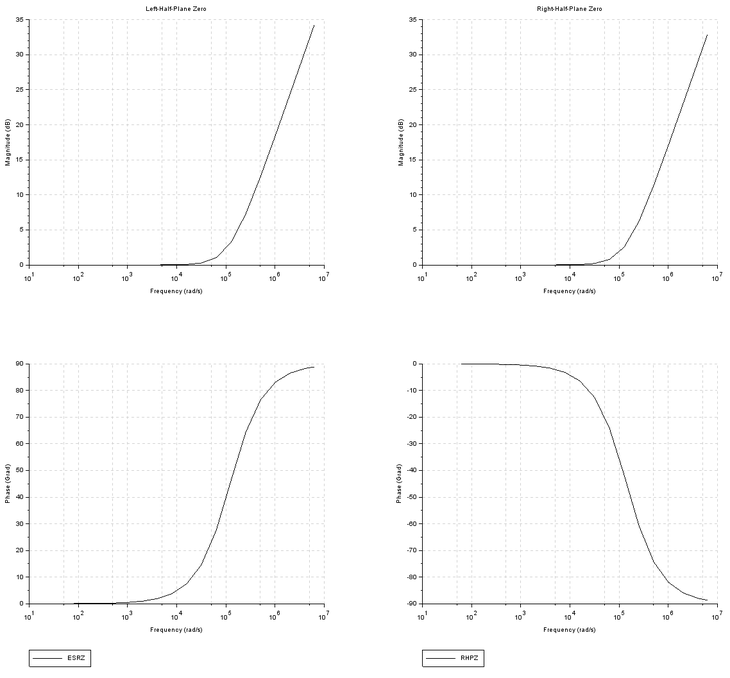

11. Sprungantworten der Teilstrecken wie LC(PT2), RL(PT1->RHPZ), ESRC(PT1->ESRZ/LHPZ)

Es kann ausgewaehlt werden welche Art von Regelung erwuenscht ist:

1. Voltage mode control.

2. Current mode control.

2.1 Peak current mode control.

2.2 Average current mode control.

Desweiteren kann entschieden werden ob das Geraet im kontinuierlichen Modus, diskontinuierlichen Modus, oder beides betrieben werden soll. Fuer den Fall das das Geraet auch bei z.B. "light load" im diskontinuierlichen Modus arbeiten soll, werden zwei Reglersaetze berechnet. Es werden die dazugehoerigen Bode Diagramme (mit/ohne Asymptoten) und Ortskurven berechnet und ausgegeben (Strecke, Regler, open loop, closed loop).

Es werden Bodediagramme unter verschiedenen Betriebsbedingungen ausgegeben, worst case bis best case, High load bis no load (wichtig wegen der RHPZ, wenn vorhanden, wie z.B. bei Boost, Sperrwandler, Sepic und Buck-Boost Topologie), denn diese wandert bei light load in Richtung niedrigerer Frequenzen und verringert den Phasenrand.

Es wird ein Schaltplan der Topologie wie als auch der Reglerstruktur ausgegeben.

Mit diesen Informationen kann das SMPS in einem Spice Simulator aufgebaut und weiter geprueft werden.

Bestimmte Zusatztools wie code generator fuer embedded digitale Regler erfordern das Wissen der Nullstellen sowie der Polstellen.

Diese werden dazu gesondert ausgegeben.

Das bedeutet konkret:

1. Pol/Nullstellen der Strecke

2. Pol/Nullstellen des kompensierenden Reglers.

Das bedeutet, Strecken- sowie Regler-Uebertragungsfunktion im Bildbereich in faktorisierter statt polinominaler Schreibweise. Auch tabellarische Ausgabe ist moeglich wegen einer eventuellen Weiterverarbeitung.

Es gibt optionale Plugins fuer

1. konkrete Auslegung von Speicherdrosseln.

2. konkrete Auslegung von Transformatoren.

3. Berechnung und Auslegung des zu der berechneten Topologie dazugehoerigen EMV Eingangsfilter.

4. Berechnung Kuehler (Wasser/Gas).